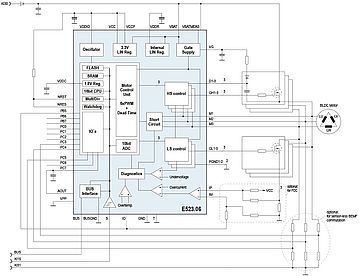

E523.06 is a BLDC motor system-in-a-chip including a 16bit CPU core. It controls 3 NMOS half-bridges for driving BLDC motors, DC motors, or other loads. CPU architecture and motor driver peripherals are optimized for single shunt FOC (Field... read more

E523.06 is a BLDC motor system-in-a-chip including a 16bit CPU core. It controls 3 NMOS half-bridges for driving BLDC motors, DC motors, or other loads. CPU architecture and motor driver peripherals are optimized for single shunt FOC (Field Oriented Control). The IC includes a high-speed single shunt foot current measurement and protects against over-current (threshold continuously adjustable), over-temperature, over- and under-voltages and short-circuits (on the fly programmable thresholds for each FET). End-of-line programming is possible via JTAG or high-speed LIN. Highest performance is provided by a 16bit CPU. A co-processor for ADC tasking automatically collects all analog system information synchronously to the output PWM. These processing units optimize system performance, system reliability, EMC performance, current dissipation and development time. The system clock is tunable in very fine steps to improve EMC behaviour and spread spectrum is supported by on-chip hardware. An adjustment of the system clock of a LIN-master is possible. The E523.06 is suited for all commutation algorithms such as trapezoid, CZCD (Current Zero-Crossing Detection) and FOC (Field-Oriented Control). Single-shunt FOC is supported by the on-board high speed current amplifier and SARADC co-processor.